안녕하세요

오늘은 삼성의 차세대 메모리반도체 인터페이스 CXL에 대해 소개해드리겠습니다.

◈반도체란? (半導體, semiconductor)

물질은 전기가 통하는 도체와 통하지 않는 부도체로 나뉩니다. 삼성전자에서 주력으로 생산하고 있는 메모리 반도체는 전압에 따라 전류를 흘릴 수도 차단할 수도 있기에 반도체라고도 불리는 스위칭 소자입니다.

DRAM은 전류의 흐름을 제어할 수 있는 스위칭 트랜지스터 소자와 전하를 저장할 수 있는 캐페시터로 구성되며 원하는 영역에 전하를 축적하면 1로 인식하는 방법으로 2진수(0과 1)로 데이터를 저장하는 장치입니다.

메모리 반도체는 고속 동작하는 CPU와 주변 장치 간 데이터 통로 역할을 수행하며 고용량과 고속 동작이 요구됩니다. 메모리 반도체를 고용량으로 만들기 위해서는 칩 내부에 더 많은 트랜지스터와 캐패시터를 넣어야 하는데 이러한 집적도를 높이는 단위가 흔히 말하는 나노 단위의 선폭 미세화 기술입니다. 집적도가 높아지면 반도체를 만들기 위한 동그란 웨이퍼 기판 위에 더 많은 반도체를 만들 수 있어 원가 절감도 가능하며 이 집적도 향상 기술에 있어 우위를 점하던 삼성전자가 기술 난이도 증가로 기술격차기 좁혀지고 있는 상황입니다.

◈CXL MEMORY

메모리 동작은 용량 증가와 동시에 고속 동작 또한 필수 조건입니다. 지금까지 SDR에서 DDR 동작으로 인터페이스가 진화하여 DDR1 - DDR2 - DDR3 - DDR4 - DDR5까지 데이터 처리 속도를 높이고 있지만 최근 인공지능과 로봇기술, 자율주행, 메타버스 등 기술 발달 속도에 따라 기하급수적으로 늘어나는 데이터 처리를 감당하기에는 역부족입니다. 많은 양의 데이터를 Access 하는 과정에서 데이터 병목현상이 발생하고 이러한 메모리의 제약을 극복하는 대표적 기술이 Memory에 연산기능을 추가하는 것이며 PIM, PNM 두 가지 종류로 개발되고 있습니다.

▶PIM 기술

PIM 약자는 processing in memory로 연산기능을 가지는 메모리입니다. 데이터를 읽어들이는데 소요되는 시간 대비 처리를 위한 시간이 수백 배 이상 빠르기 때문에 연산을 통해 효율적인 데이터 처리능력을 갖추도록 구성한 메모리입니다.

▶PNM 기술

PNM이란 Process Near Memory로 PIM과 마찬가지로 연산기능을 가지는데 칩 내부가 아닌 인접한 시스템을 활용하여 개발 난이도를 낮추고 원가를 절감할 수 있는 기술입니다.

PIM, PNM 기술 모두 메모리와 CPU 간 속도 차이를 인터페이스적 변경으로 개선하는 기술이고 CXL 메모리

CXL 약자는 Compute Express Link 입니다. CXL 컨소시엄에 설명된 CXL을 한마디로 정의한 영문은 The Breakthrough CPU-to-Device Interconnect로 CXL은 단순히 메모리 저장 기능이 아닌 연결 또는 링크의 의미를 포함합니다. 즉, 메모리가 다른 시스템과 데이터를 주고받는 인터페이스 방식 중 한 가지입니다. 기존 DDR 인터페이스의 메모리 용량확장 제약과 데이터 병목현상을 획기적으로 개선할 수 있다는 장점을 가집니다.

CXL의 자세한 내용은 아래 CXL Consortium 홈페이지를 통해 학습하실 수 있습니다.

https://www.computeexpresslink.org/

HOME | Compute Express Link

Compute Express Link™ (CXL™) is an industry-supported Cache-Coherent Interconnect for Processors, Memory Expansion and Accelerators. The CXL Consortium is an open industry standard group formed to develop technical specifications that facilitate brea

www.computeexpresslink.org

CXL 컨소시엄에 소개된 CXL 관련 자료를 참조하여 이해하기 쉽게 요약해 본 CXL 특성입니다. CPU와 메모리 간 Protocol은 cxl.io, cxl.mem, cxl.cache로 구분됩니다. 개발 단계로 구분해 보면 CXL 1.0에서 2022년 3.0 Revision까지 발표된 상태입니다.

①2019년 3월 CXL 1.0 발표 : I/O (CXL.io, based on PCIe), caching (CXL.cache), and memory (CXL.memory)

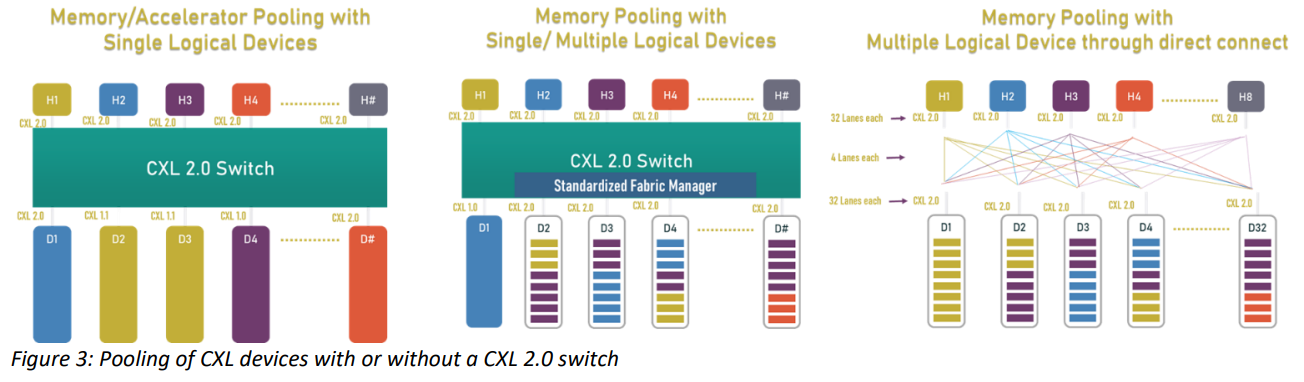

②CXL 2.0 Switch : CXL 2.0은 CXL Switch를 활용하여 여러 호스트들이 메모리를 분할하여 활용할 수 있는 인터페이스입니다. CXL Switch 기능이 없다면 각각의 메모리를 모두 개별 인터페이스로 연결해야하는 비용이 발생하며 데이터 병목현상이 발생합니다.

③CXL 3.0 : 2022년 발표된 CXL3.0 인터페이스는 Memory sharing 기능이 추가되어 기존 2.0과 달리 모든 메모리를 공유 할당 가능합니다.

위의 본문만으로는 CXL 메모리의 정체를 알기 어려울 수 있는데요. 쉬운예로 고속도로를 지나다 다른 고속도로를 이용하려면 톨게이트를 지나야 하는데 이 역할을 메모리가 수행했다면 AI, Chat GPT 등 늘어나는 데이터 처리량을 해소하기 위해 하이패스나 여러 개의 고속도로를 연결해 주는 물리적인 개선방법까지가 CXL 2.0이라고 한다면 3.0 개선에는 T-Map이나 카카오네비를 활용해 원활한 소통 경로까지 인터페이스가 처리해 주는 동작이라고 정리할 수 있습니다.

이렇게 설명해도 쉽게 이해가 안되는 사람이 대부분일 텐데요. 아래 영상은 삼성전자 개발자들이 메모리 인터페이스와 CXL에 대해 간단히 소개한 영상이므로 참고 가능합니다.

https://youtu.be/NNQDx9 y0 nYo

이제 기초가 잡혔다면 CXL 컨소시엄에서 소개하는 CXL 인터페이스의 정체를 자세히 알아볼 수 있는 영상을 추가 공유드립니다. 원어로 촬영되었지만 자막 기능을 활용하여 학습 가능합니다.

지금까지 새로운 메모리 인터페이스 CXL에 대해 알아보았습니다. 메모리 인터페이스 외에 차세대 메모리로 스위칭 소자의 변경 또한 검토되고 있는데 아래 GAA 기술에 대해서도 참고 부탁드립니다.

2023.02.10 - [유용한 생활 정보] - GAA(Gate All Around) 차세대 반도체와 삼성전자 vs TSMC

GAA(Gate All Around) 차세대 반도체와 삼성전자 vs TSMC

안녕하세요. 오늘은 전 국민이 투자하고 있는 삼성전자 주주로서 차세대 트랜지스터로 각광받고 있는 FINFET의 대체 GAA 공정에 대해 소개해 드립니다. ◈반도체의 구분 반도체는 메모리와 비메모

lawofnumber.tistory.com

'유용한 생활 정보' 카테고리의 다른 글

| Playground AI 무료 이미지 자동 생성하는 방법 (1) | 2023.05.12 |

|---|---|

| 해밍코드 원리와 패리티 연산을 활용한 ECC 에러 검출 원리 (0) | 2023.04.30 |

| 공익직불제 신청방법과 지원대상 영농일지 작성하기 (1) | 2023.04.12 |

| 티스토리 블로그 카테고리 옮기기 (0) | 2023.02.11 |

| GAA(Gate All Around) 차세대 반도체와 삼성전자 vs TSMC (0) | 2023.02.10 |

댓글